# vBNG dataplane in P4-programmable FPGA-based acceleration card

Viktor Puš, Netcope Technologies

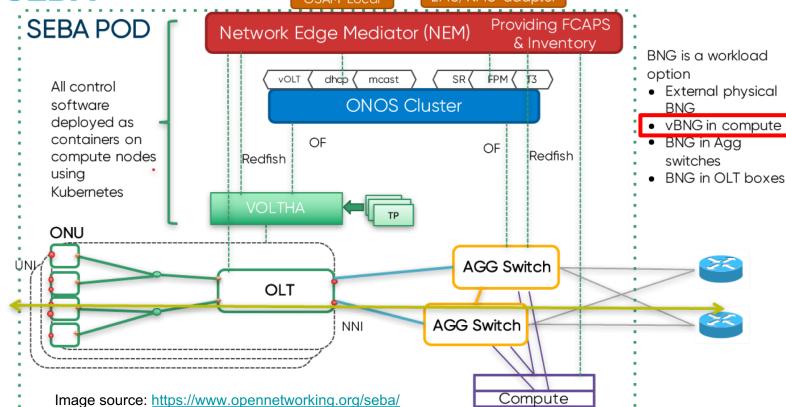

#### **BNG in SEBA**

Subscriber traffic 'fast-path' to Internet

#### **vBNG** in compute

- √ Software flexibility upgrade, bugfix, customize

- √ Scales with the number of servers (assuming load balancing)

- √ Can be standalone

CAPEX, OPEX per Gbps?

## Our plan

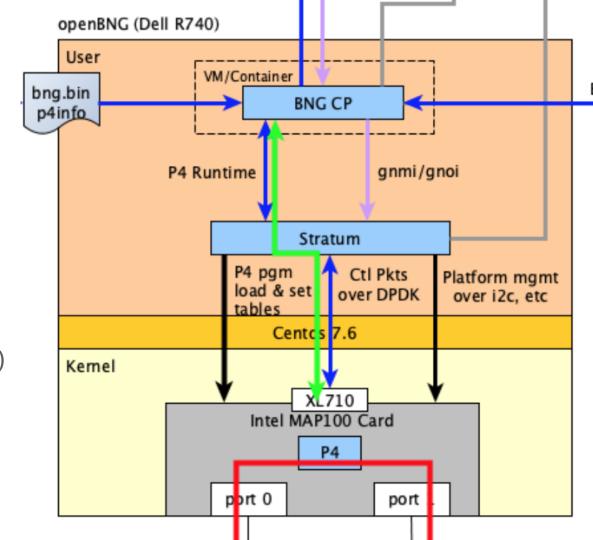

FPGA accelerators available as a config option when buying a server.

Use commodity servers with FPGA accelerator to run optimized vBNG.

Use P4 to implement the vBNG data plane in FPGA.

Use CPU cores to run vBNG control plane.

### **Ecosystem**

#### **vBNG** Architecture

Most traffic **processed only in FPGA** (red)

First packets and exception traffic (ex. DHCP) **forwarded locally** to control plane (green)

### **vBNG** pipeline in FPGA

Using P4 code from <a href="https://github.com/opencord/p4se">https://github.com/opencord/p4se</a>

- Complex

- ~30 Match Action Tables

- ~25 Counter arrays

- Many #ifdefs (INT, IPv6, SPGW, VRF, ...)

- Does not cover features outside P4 language spec (QoS)

- Set as output metadata

## Results (focused at P4 on FPGA)

Features

Throughput

Subscribers

#### **Next Steps**

#### Use on-board DRAM to implement

- Large-capacity tables

- Millions of entries

- => Support more subscribers

- HQoS

- Separate FPGA module, controlled by P4 output metadata

#### Full integration

Using open standards for extensibility (P4, P4Runtime, DPDK)

## Thank you for attention.

www.netcope.com

Find us.